Scene 1 (0s)

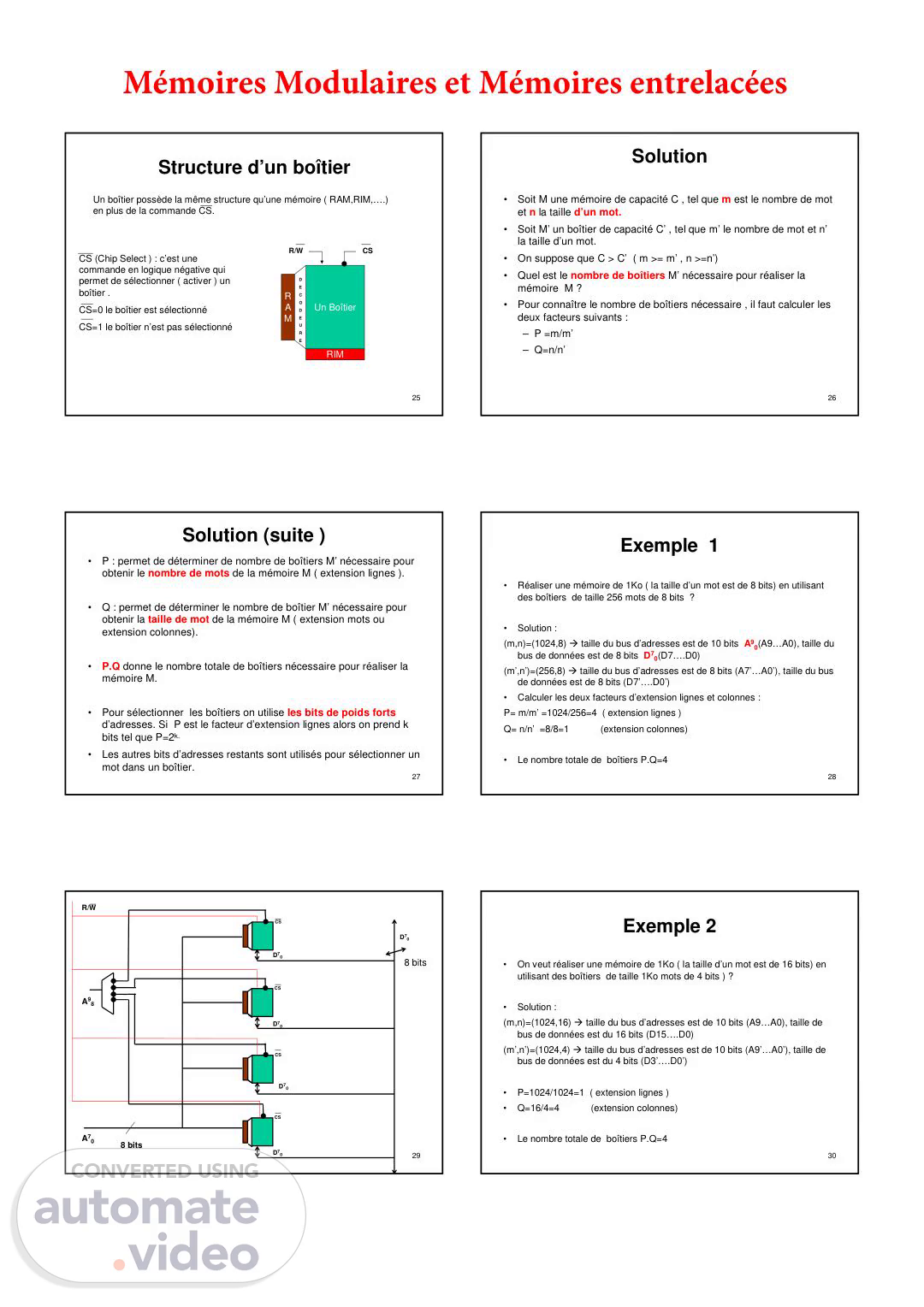

25 Structure d’un boîtier Un Boîtier RIM R A M D E C O D E U R E R/W CS CS (Chip Select ) : c’est une commande en logique négative qui permet de sélectionner ( activer ) un boîtier . CS=0 le boîtier est sélectionné CS=1 le boîtier n’est pas sélectionné Un boîtier possède la même structure qu’une mémoire ( RAM,RIM,….) en plus de la commande CS. 26 Solution • Soit M une mémoire de capacité C , tel que m est le nombre de mot et n la taille d’un mot. • Soit M’ un boîtier de capacité C’ , tel que m’ le nombre de mot et n’ la taille d’un mot. • On suppose que C > C’ ( m >= m’ , n >=n’) • Quel est le nombre de boîtiers M’ nécessaire pour réaliser la mémoire M ? • Pour connaître le nombre de boîtiers nécessaire , il faut calculer les deux facteurs suivants : – P =m/m’ – Q=n/n’ 27 Solution (suite ) • P : permet de déterminer de nombre de boîtiers M’ nécessaire pour obtenir le nombre de mots de la mémoire M ( extension lignes ). • Q : permet de déterminer le nombre de boîtier M’ nécessaire pour obtenir la taille de mot de la mémoire M ( extension mots ou extension colonnes). • P.Q donne le nombre totale de boîtiers nécessaire pour réaliser la mémoire M. • Pour sélectionner les boîtiers on utilise les bits de poids forts d’adresses. Si P est le facteur d’extension lignes alors on prend k bits tel que P=2k. • Les autres bits d’adresses restants sont utilisés pour sélectionner un mot dans un boîtier. 28 Exemple 1 • Réaliser une mémoire de 1Ko ( la taille d’un mot est de 8 bits) en utilisant des boîtiers de taille 256 mots de 8 bits ? • Solution : (m,n)=(1024,8) � taille du bus d’adresses est de 10 bits A9 0(A9…A0), taille du bus de données est de 8 bits D7 0(D7….D0) (m’,n’)=(256,8) � taille du bus d’adresses est de 8 bits (A7’…A0’), taille du bus de données est de 8 bits (D7’….D0’) • Calculer les deux facteurs d’extension lignes et colonnes : P= m/m’ =1024/256=4 ( extension lignes ) Q= n/n’ =8/8=1 (extension colonnes) • Le nombre totale de boîtiers P.Q=4 29 CS CS A9 8 CS CS A7 0 D7 0 D7 0 D7 0 D7 0 R/W 8 bits D7 0 8 bits 30 Exemple 2 • On veut réaliser une mémoire de 1Ko ( la taille d’un mot est de 16 bits) en utilisant des boîtiers de taille 1Ko mots de 4 bits ) ? • Solution : (m,n)=(1024,16) � taille du bus d’adresses est de 10 bits (A9…A0), taille de bus de données est du 16 bits (D15….D0) (m’,n’)=(1024,4) � taille du bus d’adresses est de 10 bits (A9’…A0’), taille de bus de données est du 4 bits (D3’….D0’) • P=1024/1024=1 ( extension lignes ) • Q=16/4=4 (extension colonnes) • Le nombre totale de boîtiers P.Q=4 Mémoires Modulaires et Mémoires entrelacées.

Scene 2 (1m 5s)

31 A9 0 D15 0 CS D15 12 R/W 10 bits CS D11 8 CS D7 4 CS D3 0 16 bits 32 Exemple 3 • On veut réaliser une mémoire de 1KO ( la taille d’un mot est de 8 bits) en utilisant des boîtiers de taille 256 mots de 4 bits ) ? • Solution : (m,n)=(1024,8) � taille du bus d’adresses est de 10 bits (A9…A0), taille du bus de données est de 8 bits (D7….D0) (m’,n’)=(256,4) � taille du bus d’adresses est de 8 bits (A7…A0), taille du bus de données est de 4 bits (D3….D0) • P=1024/256=4 ( extension lignes ) • Q=8/4=2 (extension colonnes) • Le nombre totale de boîtiers P.Q=8 33 CS CS CS CS A9 8 CS CS CS CS A7 0 D7 4 D3 0 D7 0 D3 0 D3 0 D3 0 D7 4 D7 4 D7 4 R/W 8 bits 8 bits 34 Exercice • Réaliser une mémoire de 8K X12 ( la taille d’un mot est de 12 bits) en utilisant des boîtiers de taille 2048 mots de 4 bits ) ? 35 Architectures des mémoires centrales 36 • Dans une architecture à un seul processeur : le processeur à l’exclusivité d’accéder à la mémoire. Le rendement de l’UC n’est conditionnée que par le temps d’accès à la MC. Demande de la lecture Disponibilité de l’information UC inactive Mémoire Centrale Processeur.

Scene 3 (1m 46s)

37 • Si le calculateur possède plusieurs processeurs qui fonctionnent en parallèle ( en même temps ), c’est possible que deux processeurs ou plus demandent d’accéder à la mémoire à la même instant. • Si la mémoire est structurée en un seul bloc alors un processeur peut monopoliser la MC. • Même si le temps d’accès est très petit, des processeurs vont être pénalisés � donc la structure de la MC est aussi importante. P1 P2 P3 P4 MC 38 1 Mémoire modulaire P1 M4 M3 M2 M1 P2 P3 P4 MC •La solution est de découper la mémoire en plusieurs modules. •Plusieurs bus permettent d’accéder simultanément (en même temps) à la MC. •Possible d’avoir autant d’accès que de modules. •On ne peut pas accéder simultanément à un module. Remarques : •Les adresses à l’intérieur d’un module sont séquentiels ( successives ) •C’est possible qu’un module soit réaliser avec des boîtiers de taille inférieur ( il faut calculer les facteur d’extension lignes et colonnes ) 39 Comment sélectionner un mot dans une architecture modulaire ? • L’adresse est divisée en deux parties : – Les bits de poids forts pour sélectionner un module. Si le nombre de module est égale à n , alors il faut prendre k bits tel que 2k >= n – Les bits de poids faibles pour sélectionner un mot dans un module. N°module adresse mot 40 Exemple • Soit une mémoire de taille de 4 Ko. Cette mémoire est découpée en 4 modules. Donner le schéma de cette mémoire en utilisant des boîtiers de 1 Ko? • Solution : • Capacité = 4 Ko = 4* 210 = 212 � la taille du bus d’adresses est de 12 bits ( A11 0). • 4 modules � 2 bits du poids forts pour la sélection des modules ( A11 10) • Les autres bits pour la sélection d’un mot dans un module ( A9 0) 41 CS CS A11 10 CS CS A9 0 D7 0 D7 0 D7 0 D7 0 R/W 10 bits D7 0 Module 0 Module 1 Module 2 Module 3 8 bits 42 • Exercice 1 : Soit une mémoire de taille de 4 Ko. Cette mémoire est découpée en 4 modules. Donner le schéma de cette mémoire en utilisant des boîtiers de 512 mots de 8 bits? • Exercice2 : Soit une mémoire de taille de 4 Ko. Cette mémoire est découpée en 4 modules. Donner le schéma de cette mémoire en utilisant des boîtiers de 512 mots de 4 bits?.

Scene 4 (2m 51s)

43 2 Mémoire entrelacée • Avec une MC modulaire , c’est possible qu’un processeur monopolise un module ( par exemple il accède a des adresse consécutive ), Pour éviter ce problème : – Un module est divisé en plusieurs Blocs . – les adresses consécutive sont placé dans des bloc différents . – Le nombre de blocs représente le degré d’entrelacement. 44 Sélectionner un mot dans une MC entrelacée • L’adresse est divisée en deux parties : – Les bits de poids faibles pour sélectionner le bloc. Si on dispose de n bloc , il faut prendre k bits tel que 2k>=n. – Les bits de poids forts pour sélectionner le mot dans le bloc . Adresse du mot N°bloc 45 Exemple 1 : une mémoire entrelacée avec un degré d’entrelacement égale à 4 , un bloc est de taille de 4 mots Bloc 0 • 4 blocs et la taille d’un bloc est égale à 4 mots de 4 bits � taille de la mémoire est égale à 16 mots de 4 bits. •Il existe 4 blocs � 2 bits de poids faibles pour la sélection A1 0 •Les bits de poids forts ( A3 2) pour sélectionner un mot dans un bloc. •L’adresse 0000 � bloc 0 ( bits poids faible 00) •L’adresse 0001 � bloc 1 ( bits poids faible 01) •L’adresse 0010 � Bloc 2 •L’adresse 0011 � Bloc 3 •L’adresse 0100 � Bloc 0 •……….. •……….. 0000 0100 1000 1100 Bloc 1 0001 0101 1001 1101 Bloc 2 0010 0110 1010 1110 Bloc 3 0011 0111 1011 1111 46 Exemple 2 • Réaliser une mémoire de capacité 512 mots de 8 bits avec des boîtiers de 128 mots de 8 bits avec un degré entrelacement de 4. • Capacité 512 =29 ( taille de bus d’adresses =9 ) • Taille d’un mot =8 � taille du bus de données =8 • 4 blocs � taille d’un bloc = 512/4 =128 • Taille d’un boîtier = 128 *8 � un boîtier par bloc est suffisant • 2 bits de poids faibles pour la sélection d’un bloc A1 0 • Les bits de poids fort ( A8 2) pour sélectionner un mot dans un bloc. 47 CS CS A1 0 CS CS A8 2 D7 0 D7 0 D7 0 D7 0 R/W 7 bits D7 0 Bloc 0 Bloc 1 Bloc 2 Bloc 3 8 bits 48 Exercices • Exercice 1 : Réaliser une mémoire de capacité 512 mot de 8 bits avec des boîtiers de 64 mots de 8 bits avec un degré entrelacement de 4. • Exercice 1 : Réaliser une mémoire de capacité 512 mot de 8 bits avec des boîtiers de 64 mots de 4 bits avec un degré entrelacement de 4..

Scene 5 (3m 56s)

49 3 Les mémoires modulaires entrelacées • La MC est divisée en plusieurs modules • Chaque module est divisé en n Blocs ( n le degré d’entrelacement) • Pour sélectionner un mot : – Il faut sélectionner le module ( bits de poids forts ) – Sélectionner le bloc dans le module ( bits de poids faibles ) – Sélectionner le mot dans le bloc ( les bits restant ) N°module adresse mot N°Bloc 50 Exemple • Réaliser une mémoire de 64 mots de 8 bits organisé en deux modules entrelacé , l’entrelacement se fait à l’intérieur ( D=2). En utilisant des circuits ( boîtiers ) de 16 mots de 8 bits. • La taille du bus d’adresses k= 6 ( 64=26) � A5 0 • Le nombre de module m=2 , la taille d’un module est égale à 32 mots. • Le nombre de bits pour sélectionner un module est égale à 1 (A5 ). • Le nombre de blocs dans un module D=2 � le nombre de bits nécessaire pour sélectionner un bloc est égale à 1 (A0 ) • la taille d’un bloc est égale 16 mots � un circuit suffit pour réaliser un bloc • Le nombre de bits nécessaire pour sélectionner une mot dans le bloc est égale à 4 (A4 1 ) 51 CS CS A5 CS CS A4 1 D7 0 D7 0 D7 0 D7 0 4 bits D7 0 A0 Module 0 Bloc 0 Bloc 1 Bloc 0 Bloc 1 Module 1 M0 M1 B0 B1 8 bits 52 N°module: X adresse mot: XXXX N°Bloc: X.